Barcelona, 4 October 2017.- BSC researchers have published the first detailed and reliable timing parameters of Spin-Transfer Torque Magnetic Random Access Memory (STT-MRAM) main memory, enabling a reliable system-level simulation of this technology. The parameters were presented today at the conference titled The International Symposium on Memory Systems 2017 (MEMSYS) which is taking place on 2-5 October 2017 in Washington DC. BSC’s approach for the STT-MRAM main memory simulation converged through research cooperation with Everspin Technologies Inc., the worldwide leader in the STT-MRAM design and manufacturing.

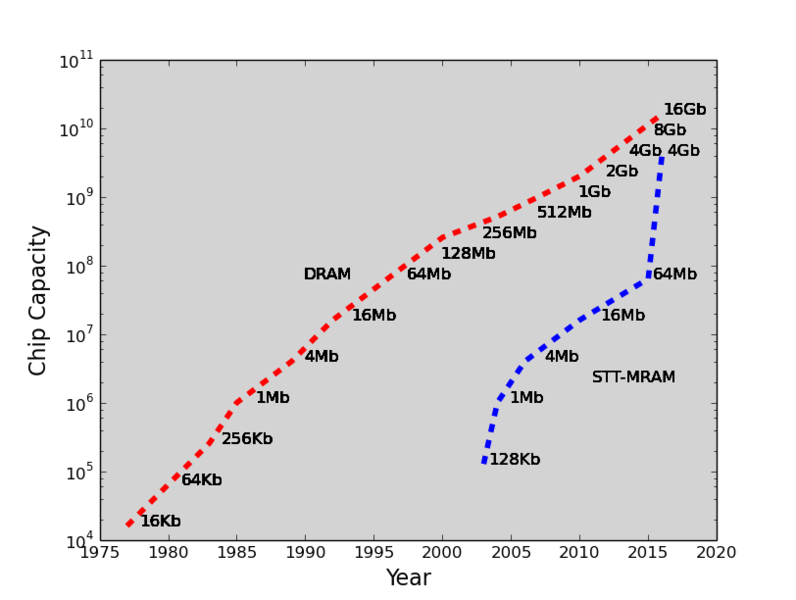

STT-MRAM is a promising new memory technology with very desirable set of properties such as non-volatility, byte-addressability and high endurance. It has the potential to become the universal memoryem> that could be incorporated to all levels of memory hierarchy. As a main memory, STT-MRAM is rapidly catching up with the mature DRAM technology, as shown in Figure 1; as a result, it has attracted significant attention from a number of major memory manufacturers. However, today academic research of STT-MRAM main memory remains marginal, mainly because the detailed STT-MRAM timing parameters have neither been standardized nor released by any industry. Researchers are therefore still struggling to conduct a reliable STT-MRAM main memory simulation.

“An intensified effort in STT-MRAM research by the memory manufacturers may indicate that a revolution with STT-MRAM memory technology is imminent, and we can expect to see a lot of exciting developments with this memory technology in the near future. Now, with the reliable detailed timing parameters published, we would strongly encourage academia to explore opportunities this technology has to offer,” concludes Petar Radojkovic, Memory Systems for HPC team leader at BSC.

In order to overcome this issue, BSC’s study thoroughly analyses and publishes detailed STT-MRAM main memory timing parameters in order to enable a reliable system-level simulation of this technology. The study is based on the fact that STT-MRAM main memory devices are and will be incorporated into the DDRx interface and protocol, indicating that most of the timings will not change from DRAM to STT-MRAM main memory. For the parameters that will change due to differences in DRAM and STT-MRAM storage cell, the best thing to do at this point is a sensitivity analysis on these parameters. The study also suggests reasonable ranges for these timings that are verified against commercially available products.

Finally, BSC Computer Science researchers seamlessly incorporate STT-MRAM timing parameters into DRAMSim2 memory simulator and use it as a part of the simulation infrastructure of the high-performance computing systems.

The results of these simulations show that STT-MRAM main memory would provide performance comparable to DRAM systems, while opening up various opportunities for HPC system improvements.

These results are also part of the European project ExaNoDe (European Exascale Processor & Memory Node Design).